Tipos de cartuchos de NES

Sumario

- 1 Introducción

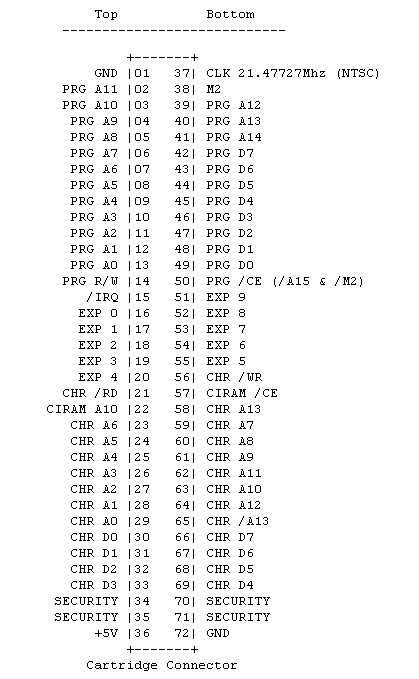

- 2 Asignación de terminales del conector del cartucho

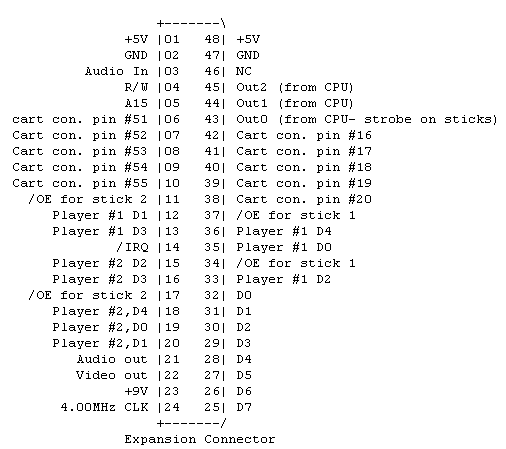

- 3 Asignación de terminales del conector de expansión

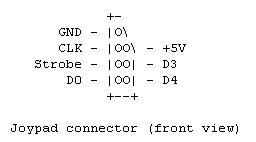

- 4 Asignación de terminales del conector del pad

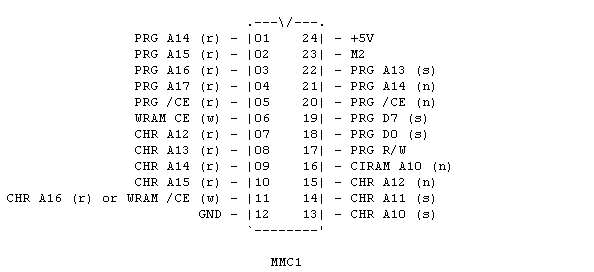

- 5 Asignación de terminales en los mappers MMCX

- 6 Intercambio de bancos mediante LS161 ( LS161 Bankswitching )

- 7 Asignación de terminales en la CPU

- 8 Asignación de terminales en la PPU

- 9 Placas bases usadas en los cartuchos

- 9.1 Placas sin intercambio de bancos

- 9.2 Placas con intercambio de bancos basado en el chip LS161

- 9.3 Placas con MMC1

- 9.4 Placas con MMC2

- 9.5 Placas con MMC3

- 9.6 Placas con MMC5

- 9.7 Placas con MMC6

- 9.8 Placas de terceras compañías

- 9.9 Placas de terceras compañías con el chip LS377

- 9.10 Placas de American Video Entertainment (AVE)

- 10 Lista de cartuchos

- 11 Notas del traductor

Introducción

He creado algunas para que el describir como funciona una NES sea más fácil. Intenté usar nombres convencionales cuando fue posible, pero no pude evitar crear algunos términos nuevos. Cuando sea posible, usare las palabras que usaba Nintendo como MMC, CHR ROM, etc.

He puesto algunos nombres genéricos para describir de forma más fácil partes de la NES.

CIRAM: Es la RAM interna de la PPU y que se encuentra situada en 0000-1FFF (2K). Es la abreviatura de "Character Internal RAM'

P-ROM: es lo mismo que la PRG ROM, o VROM.

C-ROM: lo mismo que CHR ROM.

C-RAM: equivale a CHR RAM.

Acceso a la PPU: se hace mediante A0-A13, /A13, D0-D7, /WR i /RD. A13 normalmente esta conectada a /CE de la CIRAM para así hacerla visible en las direcciones 0000-1FFF. De cualquier modo, /A13 normalmente se usa apra habilitar la C-ROM o C-RAM que hay en el cartucho (la cual se mapea en 2000-3FFF).

La CIRAM también esta relacionada con la PPU. Como se puede ver hay dos lineas de la misma para usarla. Hay muchas formas de hacerlo...

- Se puede deshabilitar toda la CIRAM poniendo a nivel alto el pin 57. Una vez hecho esto podemos situar si queremos 4K de RAM en el bus si conectamos su CE al pin 58. Hacer esto situara esos 4K de ram en 0000-1FFF. El Gauntlet 2 es un ejemplo de este caso. (Todos los cartuchos que he visto utilizan una 6264 8K RAM con A12 conectado a masa, por lo que el chip se comporta como una memoria de 4K).

- Mirroring Horizontal / Vertical . El terminal A10 de la CIRAM se llevo al conector del cartucho para permitir el mirroring . Si este terminal se conecta a A10, se tendrá mirroring vertical; pues los dos primeros bancos estarán en secuencia. Sin embargo, si se conecta a A11, el mirroring será horizontal; los bancos gemelos adyacentes serán los mismos.

- Los MMCs pueden controlar la linea de A10 de la CIRAM para cambiar tanto la pantalla o el tipo de mirroring al vuelo.

- Los mappers basados en chips LS161 pueden cambiar el estado de A10; sin embargo nadie sabe porque se querría hacer esto :-)

Asignación de terminales del conector del cartucho

Asignación de terminales del conector de expansión

Asignación de terminales del conector del pad

D0, D3 y D4 están conectados al bus a través de un buffer triestado 74368. La linea strobe va conectada al terminal 39 de la CPU. El terminal CLK va conectado al terminal /OE del buffer que a su vez esta conectado al terminal 35 de la CPU (36 si es el pad 2). Dentro de cada pad hay un registro de desplazamiento de 8 bits (4021). Para leer el estado de los botones hay que primero poner el pin 39 en alto y luego en bajo:

- LDX #$01

- STX $4016

- DEX

- STX $4016

Después de esto se debería de leer $4016 (o $4017 para el jugador 2) para obtener el estado de un botón (cada lectura desplaza un bit el registro para que el siguiente bit este presente en la siguiente lectura). Algunos juegos necesitan obligatoriamente que el valor devuelto al ejecutar LDA $4016 sea o $40 o $41, esto es debido a mala programación ya que solo hay conectados D0-D4, por lo que los tres bits superiores se suponen indeterminados. Sin embargo, si se analiza detenidamente que es lo que esta pasando se puede ver porque devuelve $40 o $41. Como las entradas a los buffers triestado pasan a nivel alto a través de unas resistencias y como el buffer es inversor, se puede ver como los 5 bits más bajos serán 0 cuando son leídos. Como D4-D1 normalmente no se usan (solo los usan la pistola y el conector de expansión) y D0 es la entrada de datos del pad, los 5 bits más bajos serán o 00000b o 00001b, dependiendo de si el botón esta pulsado (1) o no (0). Así pues, ese hecho solo se preocupa por D0-D4 ya que D5-D7 no están relacionados con la lectura del pad y por lo tanto no deberían de leerse, pero por lo visto al leerse se obtiene "010xxxxxb" (donde xxxxx es la parte del pad). Terminaremos de entender lo que pasa si analizamos los opcodes (codigos de operación) que el procesador ejecuta:

8100: $A9 ;opcode para LDA 8101: $16 ;bit bajo de la dirección 8102: $40 ;bit alto de la dirección

Como se puede ver, el ultimo byte que se pone en el bus de datos justo antes de que se pueda leer es $40 - el mismo valor que se ve cuando se lee el pad!. Esto es así debido a que las capacitancias de la linea de datos "guardan" el ultimo valor que había en ellas. La prueba de esta afirmación es bastante sencilla. En vez de ejecutar LDA $4016 , ejecutemos un LDA indirecto:

8100: LDA #$16 8102: STA $80 8104: LDA #$40 8106: STA $81 8108: LDA ($80)

Como este modo de hacerlo necesita más sitio en memoria y más ciclos para ejecutarse que un simple LDA $4016, el método indirecto no se usa. Eso si, puede ser usado para detectar si el programa esta siendo ejecutado en un emulador o no ;-) El modo correcto para leer el pad es:

8100: LDA $4016 8103: AND #$01

Esto se deshará de todos los bits inválidos y anulara cualquier posibilidad de error. El modo en que *yo * leería los pads sería este:

8100: LDY #$08 ;numero de repeticiones 8102: LDX #$01 8104: STX $4016 ;pongo a 1 el " strobe " 8107: DEX 8108: STX $4016 ;pongo a 0 el "strobe" 810B: LDA $4016 ;leo el botón 810E: ROR ;lo transfiero al bit de acarreo. 810F: TXA 8110: ROL 8111: TAX ;roto a la izquierda X, guardando el bit en la posición más baja. 8112: DEY 8113: BNE 810B ;repito 8 veces para leer los 8 botones. 8115: RTS ;devuelvo el acumulador con el estado de los 8 botones.

Este trozo de código primero hace que se "congelen" los valores de los botones pulsados, entonces recoge el estado del primer botón y el efecto de la rotación queda registrado en el bit de acarreo. Después, el registro X, se transfiere al acumulador de modo que que el valor del botón pueda ser desplazado en el. Luego se devuelve a X, y el registro y se decrementa en una unidad. Todo este proceso se repite 8 veces para crear un byte a partir del estado de los 8 botones.

Asignación de terminales en los mappers MMCX

El tipo de señales aparece entre paréntesis:

- (r) Esta linea solo va a la ROM.

- (s) Esta linea es compartida entre la ROM, el MMC y la NES.

- (n) Esta linea únicamente esta conectada al conector del cartucho, no a la ROM.

- (w) Esta linea va conectada exclusivamente a la WRAM.

MMC 1

Utiliza encapsulado de 24 PIN DIP. Tiene varias variantes: MMC1, MMC1A, MMC1B2, etc

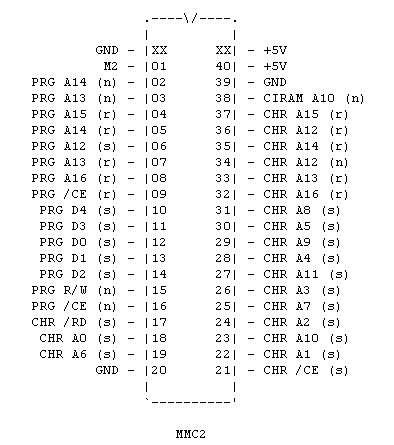

MMC 2

Utiliza encapsulado de 40/42 PIN DIP. Los pins marcados con X son opcionales y solo se usarían si el chip tuviese 42 terminales en vez de 40. Sólo existe una variante MMC2 RD387-001

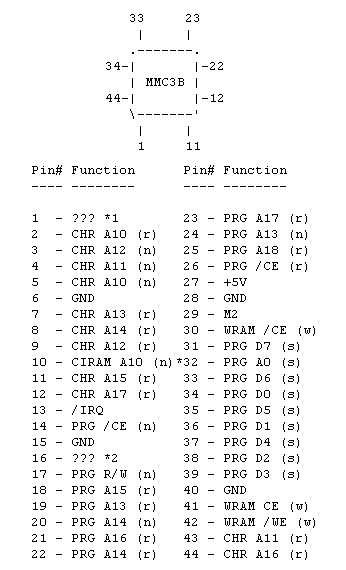

MMC 3

Utiliza encapsulado QFP de 44 PIN. Hay 3 variantes: MMC3A, MMC3B y MMC3C.

Notas:

- *n el Gauntlet no se usa.

- *1: Hay veces que el pin 1 y 2 están unidos entre si, en caso contrario el pin 1 queda sin conectar

- *2: Hay veces que el pin 16 va conectado a masa y otras en las que simplemente esta "al aire". Parece ser que los pins 1,2 y 16 están relacionados entre si; si el 1 y el 2 están cortocircuitados entonces el 15 y 16 también lo estarán. Si los pines 1 y 2 están sin conectar, también lo estarán el 15 y el 16. Nunca he visto, por ejemplo, que los pines 1 y 2 estuviesen conectados entre si, mientras que el pin 16 estaba desconectado o viceversa. Sospecho que están relacionados con la RAM extra de la sección de la CHR.

MMC 4

No se sabe de ningún cartucho que lo use.

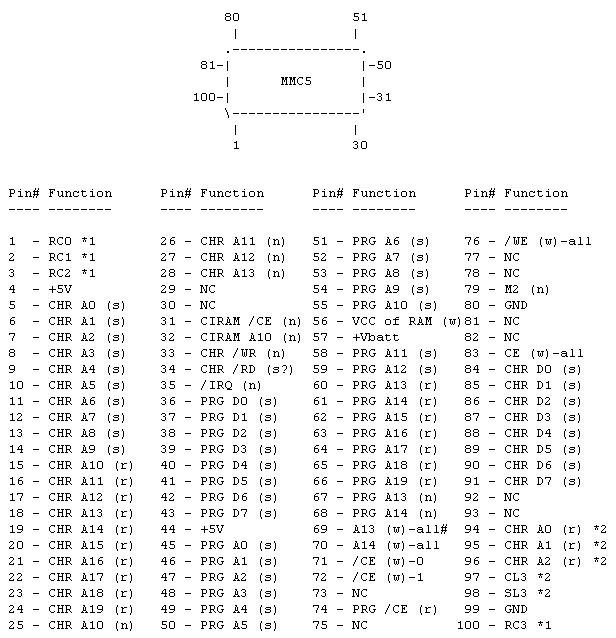

MMC 5

Utiliza encapsulado QFP de 100 PIN. Solo existe una única versión; la MMC5.

Notas

- #: la asignación de estos pins aún no ha sido confirmada y su uso se ha sacado observando los pins vecinos.

- *1: PINS 1,2,3 y 100 parecen ser algún tipo de entrada de datos. En esta placa en concreto (Castlevania 3) están sin usar y su finalidad es desconocida; sin embargo el terminal #54 del cartucho esta conectado a esta circuiteria extra y este terminal solo va al puerto de expansión que hay debajo de la NES, así que dudo que este fuese utilizado alguna vez en algún cartucho.

- *2: los pines 94 a 98 sirven para poner el cartucho en modo SL o CL. No tengo ni idea de cual es la difrencia entre los dos modos, el cartucho que he usado (Castlevania 3) estaba en modo CL.

Para ponerlo en modo CL hay que conectar CHR A0, A1, A2 de la NES a A0, A1, A2 respectivamente. Después de esto hay que conectar entre si los pines 97 y 98 y dejar los pines 94,95 y 96 sin conectar. Si lo que queremos es dejar el cartucho en modo SL entonces hemos de conectar el pin 94 del MMC5 a A0 de la CHR ROM, el 95 al A1 de la CHR ROM y la 96 a A2 de la CHR ROM. Para finalizar dejaremos el pin 97 al aire y el 98 lo conectaremos a masa.

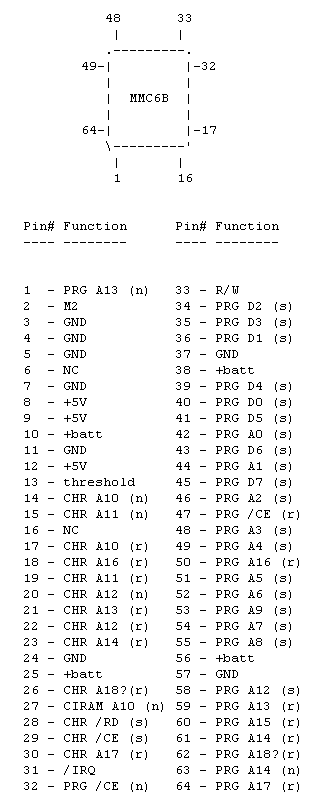

MMC 6

Utiliza encapsulado QFP de 64 PIN. Actualmente se conoce únicamente la versión MMC6B, pero sospecho que hay una versión A.

Nota: A10 y A11 no se conectan a este chip. Threshold: va conectado a un divisor resistivo entre +5V y GND. La resistencia con los 5V a uno de sus extremos es de 180 ohmios y la otra que tiene un extremo a masa, es de 470 ohmios.

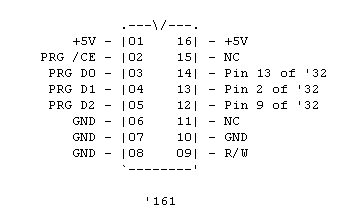

Intercambio de bancos mediante LS161 ( LS161 Bankswitching )

Hay más cartuchos de los que parece que usan el intercambio de bancos de memoria basado en el uso de un chip LS161, o en una combinación de este y de otro chip que puede ser o bien un LS32 o bien un LS02.

Los dos tipos principales de cartuchos que usan solo un chip LS161 son los siguientes:

- NES-CN-ROM-256-[O2,05]: en estos cartuchos se puede elegir tanto el mirroring H como el V. La PRG-ROM no esta bankswitched y puede tener un tamaño de 16K o 32K. La que si esta bankswitched es la CHR-ROM, que tendra un tamaño de 16K o 32K, que aparecera como 4 paginas de 8K.

- NES-BN-ROM-01: idéntica al modelo de arriba solo que utiliza una rom de 128K de 28 pines.

- NES-UN-ROM-05 / Konami #531320 : Esta placa utiliza un LS161 junto a un LS32. La rom esta configurada como un cartucho sin intercambio de bancos aunque esta vez A0-A13 va a los terminales A0-A13 de la ROM. A14 se utiliza para controlar el LS32 que sera quién le diga al procesador que banco de memoria es el que ha de ver. Cuando este terminal (A14) esta en alto, fuerza todas las lineas de dirección del intercambio de datos a alto, por lo que el procesador solo vee el ultimo banco sin importar lo otro. Si por el contrario dicho terminal está a nivel bajo, las puertas OR dejaran pasar cualquier valor que este en la otra entrada (que vendrá determinado por el valor de las salidas del LS161 pues estas están conectadas a las puertas OR). El apartado de la memoria de CHR esta cubierto por un chip de memoria RAM de 8K. La placa de Konami es idéntica técnicamente a esta y solo se diferencian minimamente en el rutado de las pistas.

- NES-AN-ROM-03: este cartucho cubre las necesidades de memoria del apartado CHR mediante un chip de memoria RAM de 8K. Para seleccionar el banco se usa un LS161 y un LS02 para deshabilitar la PRG-ROM durante cualquier escritura la circuito de intercambio de bancos. Marat se preguntaba porque el programa iba a querer escribir en una dirección asociada con un banco... pues la razón es que si cambiamos a otro banco, por el ejemplo el #05, usando este trozo de código: LDA #$05 y STA $FFF5 sin esta medida, se producirá un conflicto de bus con la ROM; la ROM tiene el valor $05 guardado en la dirección $FFF5. Así pues, esto es necesario ya que la ROM no se desconecta durante la escritura de un dato en la ronza de la ROM!!! Sin embargo, el añadir un LS02 alivia estos problemas pues desconecta la ROM durante cualquier escritura en la zona del cartucho.

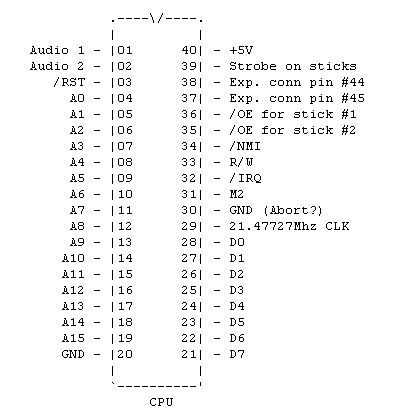

Asignación de terminales en la CPU

Los pins 39, 38 y 37 corresponden respectivamente a los bits D0, D1 y D2 de STA $4016. El pin 36 y 37 pasan a estado bajo durante un LDA $4016 y LDA $4017, respectivametne. Las etiquetas Audio 1 y Audio 2 marcan la salida de los dos canales cuadrados de audio y la de los canales de triangulo, ruido y PCM, respectivamente.

Asignación de terminales en la PPU

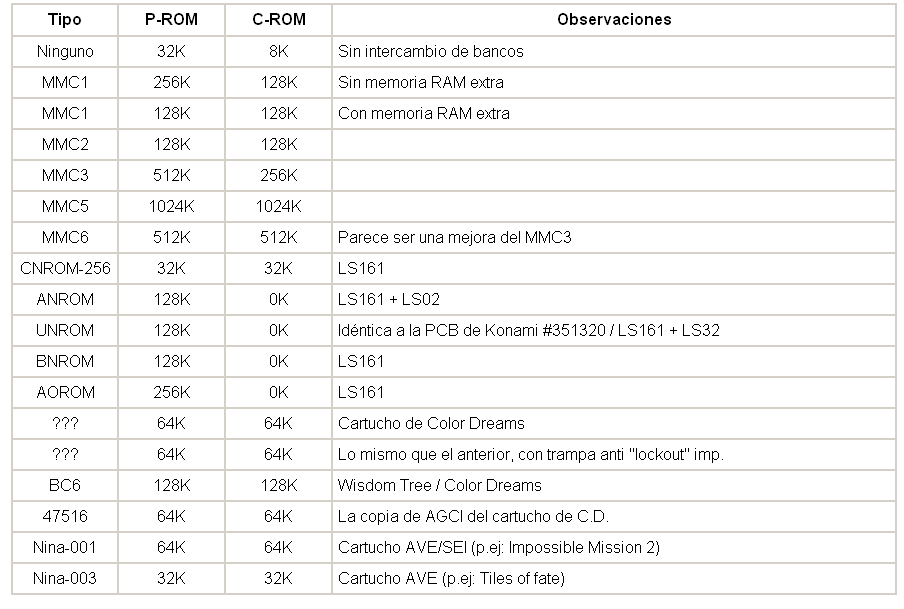

Placas bases usadas en los cartuchos

Placas sin intercambio de bancos

- NES-NROM-[01,03,05] : Esta placa es la única sin intercambio de bancos de memoria y contiene 8K de C-ROM y 32K de P-ROM

Placas con intercambio de bancos basado en el chip LS161

- NES-CN-ROM-256-02 : Esta es una de las placas base que usa el intercambio de bancos mediante el chip LS161. Puede alojar una P-ROM /C-ROM de 16 0 32 K.

- NES-ANROM-03 : Esta placa utiliza un LS161 junto a un LS02 para realizar el intercambio de bancos. El tamaño de la P-ROM es de 128K y en vez de C-ROM lleva un chip de 8K de RAM. El LS02 evita los conflictos de bus entre la CPU y la ROM

- NES-UNROM-[05,09] y 351320 : Para el intercambio de bancos utiliza un método bastante interesante basado en el uso de un LS161 y un LS32. Para conseguirlo lo que hace es partir la P-ROM en dos bancos de 16K, donde los últimos 16K siempre apuntan a los últimos 16K de la ROM. El primer banco esta bajo el control del programa. Esta placa esta ocupada por 128K de P-ROM y 8K de memoria RAM.

- NES-BN-ROM-01 : Tiene 128K de P-ROM que pueden ser intercambiados en bloques de 32K. También contiene 8K de C-RAM.

- NES-AORM-03 : Tiene 256K de P-ROM que pueden ser intercambiados en bloques de 32K. También contiene 8K de C-RAM.

Placas con MMC1

- NES-SNROM-[01,03,05,06] : Puede tener hasta 512K de P-ROM y 8 K de C-RAM. Además tiene otro chip de RAM (WRAM) situada en las posiciones 6000-7FFF del mapa de memoria de la CPU que puede ser salvaguardada mediante una batería.

- NES-SEROM-04 : puede tener tanto 16 o 32K de C-ROM y 32K de P-ROM (esta ultima no pude usar el intercambio de bancos).

- NES-SGROM-04 : tiene 8K de C-RAM y hasta 512K de P-ROM.

- NES-SLROM-04 : Hasta 256K de C-ROM y 512K de P-ROM.

- 351908 : Utiliza 128K de C-ROM y 128K de P-ROM.

Placas con MMC2

- NES-PNROM-05 : seguramente sólo fue utilizada en un cartucho. Tiene 128K de C-ROM y 128K de P-ROM, a parte del MMC2.

Placas con MMC3

- NES-TKROM-10 : contiene 8K de SRAM salvaguardada por batería, 256K de C-ROM y 512K de P-ROM.

- NES-TR1ROM-01 : una placa interesante ya que contiene 4K de RAM mapeada en la zona 0000-1FFF de la PPU (deshabilita la CIRAM), y 64K de C-ROM en la posición 2000-3FFF. El tamaño de la P-ROM puede ser de hasta 512K.

- NES-TLROM-03 : contiene hasta 256K de C-ROM y hasta 512K de P-ROM.

- NES-TSROM-[04,06,07] : El tamaño máximo de la C-ROM es de 256K mientras que el de la P-ROM llega hasta los 512K. Además contiene 8K de WRAM posicionada en las posiciones de memoria 6000-7FFF del mapa de memoria de la CPU.

- NES-TGROM-01 : tiene 8K de C-RAM con hasta 512K de P-ROM.

- 352026 (Konami) : 128K de C-ROM y 128K de P-ROM.

Placas con MMC5

- NES-ELROM-01 : a parte del MMC5 utiliza 256K de C-ROM y 256K de P-ROM.

- NES-ETROM-01 : una palabra: WOW! Esta placa ocupa toda la carcasa del cartucho! Tiene dos chips de RAM de 8K, uno de los cuales conectado a una batería, el MMC5 y una P-ROM y C-ROM de tamaño por determinar.

Placas con MMC6

- NES-HKROM-01 : utiliza un chip de 256K de C-ROM y hasta 512K de P-ROM y tiene batería. Aunque el MMC6 tiene una RAM interna de 1K parece que se comporta como un MMC3 en todos los demás apartados.

Placas de terceras compañías

- [Nº de parte # dice '(c) 1990 Color Dreams Inc.' en la parte de abajo] : esta placa utiliza un 74LS377 con el nombre del componente borrado. Por suerte tengo mi identificador de mano de los ID's de chips :-) Contiene 32K de C-ROM y 32K de P-ROM.

- [Nº de parte # dice '(c) 1991 Color Dreams Inc.' en la parte de abajo] : esta placa es muy parecida a la de antes a excepción de que usa 64K de P-ROM y 64K de C-ROM.

- BC6 (Fabricada por Color Dreams : lo mismo que las anteriores solo que el tamaño de la C-ROM y la P-ROM pasa a ser 128K.

- 47516 (Fabricada AGCI) : una placa interesante ya que es casi idéntica a las anteriores a excepción de que el chip de intercambio de bancos solo tiene el nombre de la casa que la fabricó. Tiene la misma asignación de terminales que un 74LS377 aunque no lo podre confirmar hasta que termine mi lector.

- Nina-001 (Fabricada por SEI) : Utiliza 6 chips de la familia 74 para hacer el intercambio de datos. A parte de estos chips tiene 64K de C-ROM, 64K de P-ROM, 8K de WRAM y un "anti- lockout " que curiosamente se llama "Nina".

- Nina-003 (Fabricada por AVE) : Este parece haber estar fabricado por la misma compañía que el anterior. Utiliza 3 chips de la familia 74 para hacer el intercambio de datos y el tamaño de C-ROM es de 32K y el de P-ROM de 32K.

- A800XX (Tengen) : es una placa muy extraña. Tiene un chip 'Mimic 1' para hacer el intercambio de bancos. Obviamente tiene la versión "Tengen" del chip regional. El tamaño de las ROMs es desconocido.

- Bic-48 y BIC-43 (Fabricada por Camerica) : utiliza un chip de 20 pines para el intercambio de bancos con la referencia 'BF9093'. Contiene 256K de P-ROM y 8K de C-RAM.

- Bic-62 (Fabricada por Camerica) : el chip utilizado para hacer el bankswitching esta vez viene etiquetado como 'BF9097'. Al igual que el anterior utiliza 8K de RAM para la parte CHR y 256K para la P-ROM.

Placas de terceras compañías con el chip LS377

Entre ellas se encuentran las usadas en cartuchos de Color Dreams, AGCI, Wisdom Tree, Bunch Games, etc..

- [Nº de parte #; Color Dreams] : esta placa se puede diferenciar de las otras por su forma característica forma en L. El tamaño máximo para la P-ROM y C-ROM es de 64K. La P-ROM se intercambia en bancos de 32K mientras que la C-ROM lo es en bancos de 8K. Hay un registro de un byte al cual se puede acceder escribiendo desde $8000-$FFFF para cambar los bancos. La parte baja de este byte (D0-D3) sirve para seleccionar el banco deseado de la P-ROM (cada banco es de 32K) y la alta (D4-D7) para la C-ROM (cada banco es de 8K). El mirroring esta permanentemente ajustado a Horizontal.

- [Nº de parte #; Color Dreams] : esta placa tiene 5 transistores, dos redes de resistencias, tres condensadores electrolíticos y un MAX7660CPA. Técnicamente es igual a la anterior a excepción de un circuito "anti- lockout " mejorado.

- BC6 (Colour Dreams) : Esta placa, que yo sepa, fue utilizada únicamente en los cartuchos de Wisdom Tree. Ambas P-ROM y C-ROM son de 128K. El mirroring esta ajustado permanentemente a Horizontal.

- 47156 (AGCI) : Esta es una placa totalmente copiada de la de un cartucho de Colour Dreams!. Hay tres transistores y el LS277 cuyas marcas son AGCI#1, AGCI#2, AGCI#3 (para los transistores) y AGCI# (el LS277). Es bastante gracioso ver como han copiado toda la placa hasta los valores de las piezas... la única variación es que se puede elegir el mirroring (H o V) aunque de fabrica viene ajustado a Horizontal. El tamaño máximo de las roms es de 64K.

Placas de American Video Entertainment (AVE)

Nota: la misma compañía que diseño las placas de AVE también diseño las de SEI.

- Nina-03 : utiliza un "Faux-lockout" con un encapsulado de 14 pines. Permite roms de 32K y usa dos chips TTL, un LS 175 y un LS138, para realizar el intercambio de bancos de la C-ROM (la P-ROM no se puede intercambiar). Para cambiar de bancos hay que escribir con cualquier cosa usando A14 y A8 en alto y A15 y A13 en bajo (6100-61FF, 7F00-7FFF), solo se usa D0 y D1 para indicar que banco de 8K de la C-ROM se usará.

- Nina-001 : Usa seis chips TTL; 2*LS173, LS139, LS74 y LS00. Hay 8K de WRAM, dos roms de 64K y un " faux-lockout " marcado como 'NINA'. Los 8k de WRAM están mapeados en la zona $6000-$7FFF. Se puede seleccionar el banco de P-ROM escribiendo en $7FFD. La zona de C-ROM esta partida en dos partes: $0000-$0FFF y $1000-$1FFF. Se puede elegir el banco deseado para cada zona de manera individual. El banco de $K se selecciona escribiendo en $7FFE y el banco superior mediante $7FFF. Notar que se debe de usar estas direcciones que no hay otras que se decodifiquen. Solo hay un bit usado para el banco de P-ROM y sólo 4 bits para los bancos de la C-ROM.

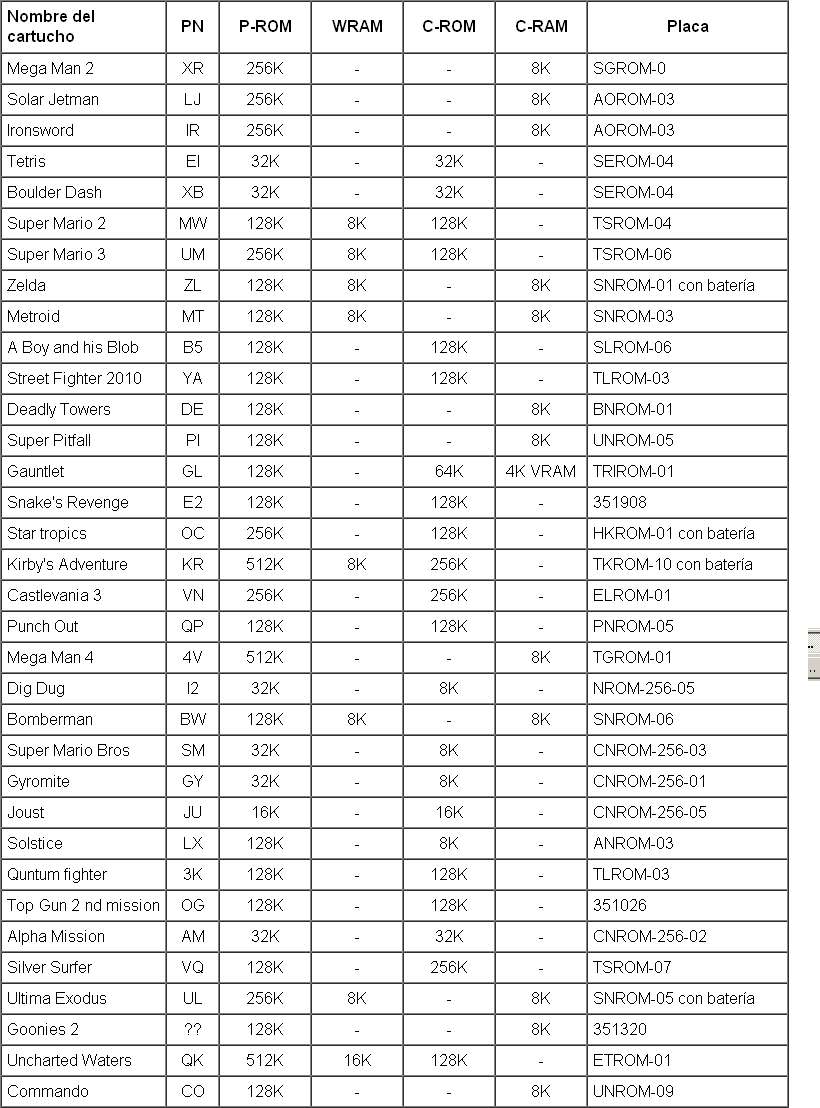

Lista de cartuchos

Nintendo

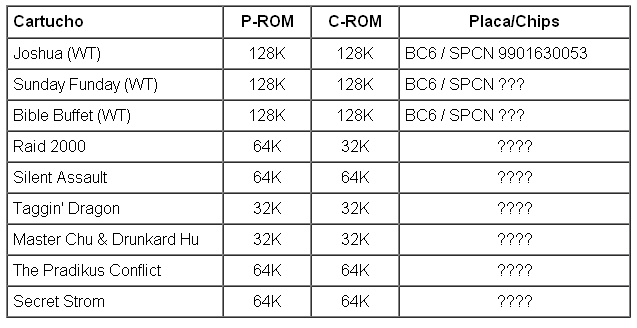

Colour Dreams (y también Wisdom Tree)

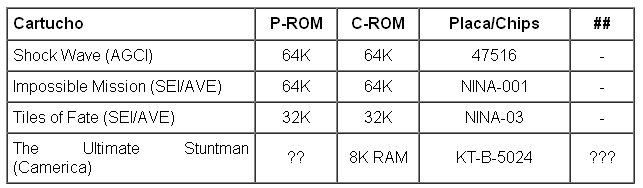

AGCI, SEI/AVE, Camerica/Code Masters

La zona de CHR universal debería ser:

8K de RAM en las posiciones 0000-1FFF intercambiables en bancos de 2K o 4K. Se debe permitir acceso con A10/A11/A12 y CE. 8K de RAM en las posiciones 2000-3FFF con acceso permitido a través de A10/A11/A12/CE/WE/OE. 12024K de C-ROM en 2000-3FFF con intercambio de bancos. Se debe permitir su intercambio en fragmentos de 2K, 4K, 8K, 16K, 32K, 64K, 128K, 256K, 512K y 1024K.

La zona universal de PRG debería de ser:

12K de RAM intercambiable en 5000-7FFF. Se debería poder desactivar segmentos de 256 bytes . 1024K de ROM intercambiable en bancos de 2K a 1024K. El controlador de intercambio de bancos debería de ser uno de estos: cualquier MMC de Nintendo, un LS377, cualquiera que use un LS161 o uno de los dos controladores de Camerica.

Notas del traductor

Todo este texto que has leído ha sido traducido directamente de lo que ha entendido el traductor cuando leyó el documento original por lo que no es una traducción literal. Es aconsejable que si tienes un nivel de ingles aceptable te leas el original ya que la traducción seguramente tendrá algún que otro error, y bueno no es necesario decir que si encuentras alguno no dudes en ponerte en contacto con él. Espero que os haya parecido interesante el documento.